Intel's Programmable Solutions Group has launched the Intel Agilex 7 FPGA, featuring the R-Tile chiplet. This groundbreaking FPGA stands as the industry's first FPGA to incorporate PCIe 5.0 and CXL capabilities, and it is also the only FPGA with hard intellectual property (IP) supporting these interfaces. The Agilex 7 FPGAs with the R-Tile chiplet deliver cutting-edge technology with 2-times faster PCIe 5.0 bandwidth and 4-times higher CXL bandwidth per port compared to other competitive FPGA products.

According to a white paper from Meta and the University of Michigan, the integration of FPGAs with CXL memory into 4th Gen Xeon-based servers while utilizing transparent page placement (TPP) and efficient page placement significantly improves Linux performance by up to 18%. Furthermore, UnifabriX demonstrated the performance benefits of their CXL-enabled Smart Memory Node through various benchmarks. One of the benchmarks revealed a 28% increase in the HPCG (high-performance conjugate gradient) score, leveraging 2-times more 4th Gen Xeon cores for HPC workloads.

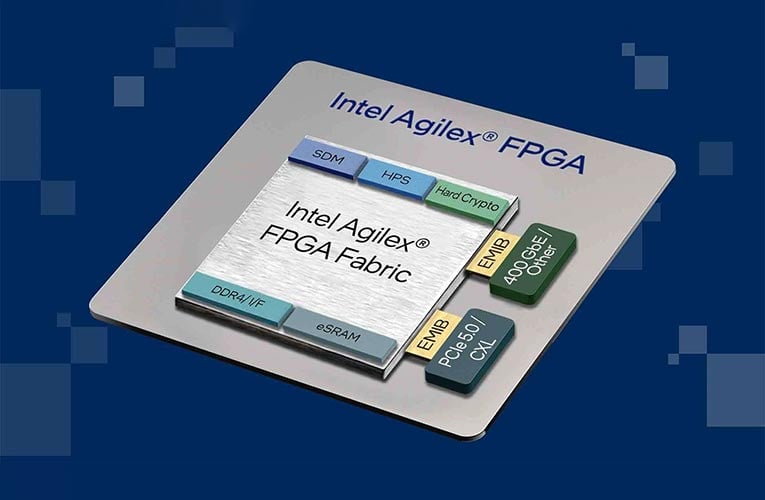

Intel Agilex® 7 FPGAs adopt a heterogeneous multi-die architecture, incorporating an FPGA fabric chiplet at the core, interconnected with transceiver chiplets using Intel's embedded multi-die interconnect bridge (EMIB) technology. Each chiplet, also referred to as a tile, represents a compact integrated circuit die containing specific hardened functionality. This innovative chiplet arrangement enables a cost-effective approach to achieve high-density interconnectivity within a single package, catering to a wide range of applications and providing customers with tailored, flexible solutions.